# Scans By Outsource-Options (NR1DX)

Outsource-Options Suite 2M 187 Depot Road, Hollis, NH 03049

<u>nr1dx@arrl.net</u> or <u>Henderson@outsource-options.com</u>

"High resolution scans of obsolete technical manuals"

If you purchased this manual from us (typically through our Ebay name of NR1DX) thank you very much. If you received this from a well-meaning "friend" for free we would appreciate your treating this much like you would "share ware". By that we mean a donation of at least \$5-10 per manual is appreciated in recognition of the time, energy and quality of effort that went into preserving this manual. Donations via PayPal go to: <a href="mailto:nr1dx@arrl.net">nr1dx@arrl.net</a> or can be mailed to us the address above. This is not a hobby for us but a semi-retirement business used to augment our diminished income in the face of the current degraded world economy.

Typically the scans in our manuals are done as follows;

- 1) Typed text pages are typically scanned in black and white at 300 dpi.

- 2) Photo pages are typically scanned in gray scale mode at 600 dpi

- 3) Schematic diagram pages are typically scanned in black and white at 600 dpi unless the original manual had colored high lighting (as is the case for some 70's vintage Tektronix manuals).

Original pages, which exceed the 8.5 x 11 format, are scanned with enough overlap so that they can be printed and pieced. This is done for primarily for two reasons, the time involved in post processing these to their original size is not trivial and most people do not have the ability to print 11 X 17 pages anyway.

If your looking for a quality scanned technical manual in PDF format please drop us a line at <a href="mailto:nr1dx@arrl.net">nr1dx@arrl.net</a>. and we will be happy to email you a current list of the manuals we have available. If you don't see the manual you need on the list drop us a line anyway we may still be able to point you to other sources. If you have an existing manual you would like scanned please write for details, This can often be done very reasonably in consideration for adding your manual to our library.

Thanks Ward Herdemon, NRTDX

Dave Henderson

Outsource-Options

#### SERVICE MANUAL

#### **SERVICE MANUAL**

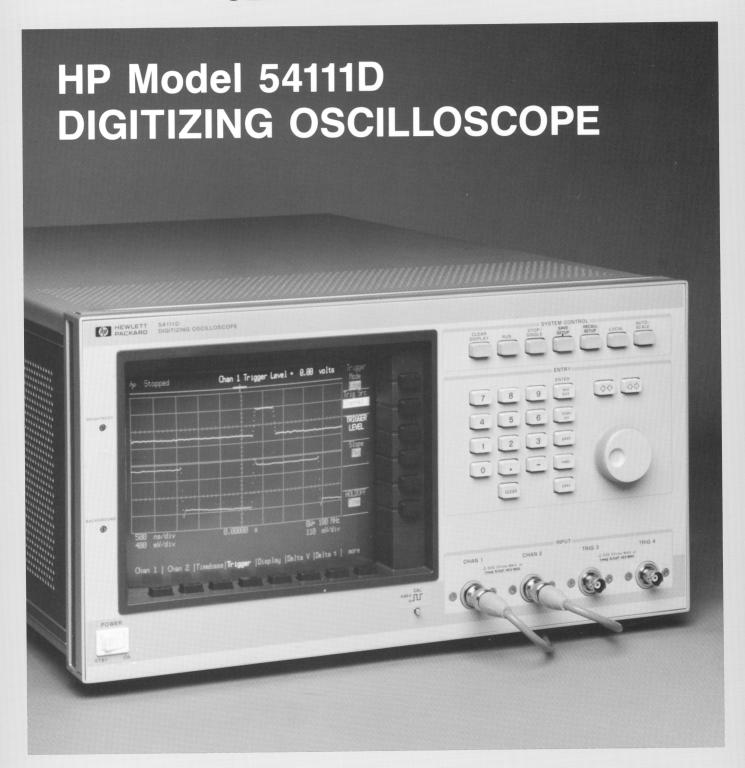

## HP 54111D DIGITIZING OSCILLOSCOPE

#### **SERIAL NUMBERS**

This manual applies directly to instruments with serial numbers prefixed:

2808A

With changes described within, this manual also applies to instruments with serial prefixes:

2640A 2710A 2726A 2733A

For additional important information about serial numbers, see INSTRUMENTS COVERED BY MANUAL in Section I.

© COPYRIGHT HEWLETT-PACKARD COMPANY/COLORADO SPRINGS DIVISION 1987 1900 GARDEN OF THE GODS ROAD, COLORADO SPRINGS, COLORADO U.S.A.

ALL RIGHTS RESERVED

Manual Part No. 54111-90912 Microfiche Part No. 54111-90812

PRINTED: June 1988

#### **CERTIFICATION**

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

This Hewlett-Packard product is warranted against defects in material and workmanship for a period of one year from date of shipment. During the warranty period, Hewlett-Packard Company will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by HP. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### ASSISTANCE

Product maintenance agreements and other \_customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

#### **TABLE OF CONTENTS**

| 1. | GENERA  | LINF                                  | DRMATION                                                                                                                      |                          |

|----|---------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|    |         | 1-1.<br>1-2.<br>1-3.<br>1-4.<br>1-5.  | Introduction  Description  Specifications  Operating Characteristics  General Characteristics                                 | 1-1<br>1-1<br>1-1<br>1-2 |

|    |         | 1-6.<br>1-7.<br>1-8.<br>1-9.<br>1-10. | Safety Considerations Instruments Covered by Manual Options Accessories Supplied Recommended Test Equipment                   | 1-2<br>1-2<br>1-2        |

| 2. | INSTALL | ATION                                 |                                                                                                                               |                          |

|    |         | 2-1.<br>2-2.<br>2-3.<br>2-4.<br>2-5.  | Introduction Preparation for Use Operating Environment Cleaning Requirements Storage and Shipment                             | 2-1<br>2-1<br>2-1<br>2-1 |

|    |         | 2-6.<br>2-7.                          | Environment                                                                                                                   |                          |

| 3. | PERFORI | MANC                                  | E TESTS                                                                                                                       |                          |

|    |         | 3-1.<br>3-2.<br>3-3.<br>3-4.<br>3-5.  | Introduction                                                                                                                  | 3-1<br>3-1<br>3-1        |

|    |         | 3-6.<br>3-7.<br>3-8.<br>3-9.<br>3-10. | Abbreviated Test Procedures  Tests After Replacements  Probes Used During Tests  Performance Test Procedures  One-key Powerup | 3-2<br>3-2<br>3-3        |

|    |         | 3-12.<br>3-13.<br>3-14.               | Calibrator Amplitude  Measurement Accuracy  Offset Accuracy  Bandwidth  Transition Time                                       | 3-5<br>3-7<br>3-10       |

|    |         | 3-16.<br>3-17.                        | Time Interval Accuracy                                                                                                        | 3-15<br>3-19             |

| 4. | ADJUSTMENTS  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | 4-1.         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-1  |

|    | 4-2.         | Adjustment Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1  |

|    | 4-3.         | Test Equipment Required                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1  |

|    | 4-4.         | Access to Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-1  |

|    | 4-5.         | One-key Powerup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1  |

|    | 4-6.         | Adjustments Required After Replacements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-2  |

|    | 4-7.         | Power Supply Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-3  |

|    | 4-8.         | Clock and Gap Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-5  |

|    | 4-9.         | Gain and Flat Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-8  |

|    | 4-10.        | and the second s | 4-10 |

|    | 4-11.        | Attenuator Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-12 |

|    | 4-12.        | Vertical Self-Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-14 |

|    | 4-13.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-14 |

|    | 4-14.        | Vertical Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-14 |

|    | 4-15.        | Probe Tip Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-14 |

|    | 4-16.        | DO Gam Majasament                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-15 |

|    | 4-17.        | Trigger Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-17 |

|    | 4-18.        | THIT COURT OF CONTRACT CONTRAC | 4-17 |

|    | 4-19.        | Throbass Troqueries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-17 |

|    | 4-20.        | Channel Skew Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-18 |

|    | 4-21.        | rigger addition rajedinents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-20 |

|    | 4-22.        | Doidy/ Later / mile Doomator / bjack in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-21 |

|    | 4-23.        | THE THIN OHOU THOU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-22 |

|    | 4-24.        | Edde Evolution and Edde State  | 4-25 |

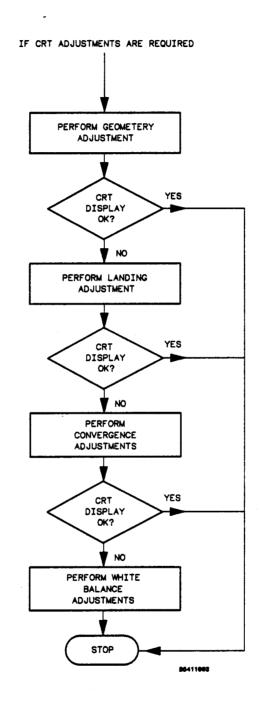

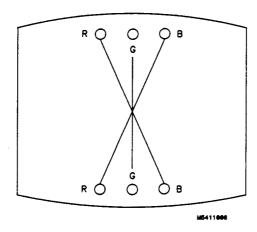

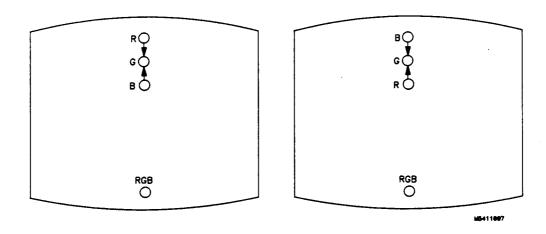

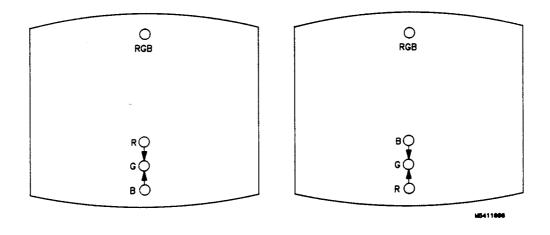

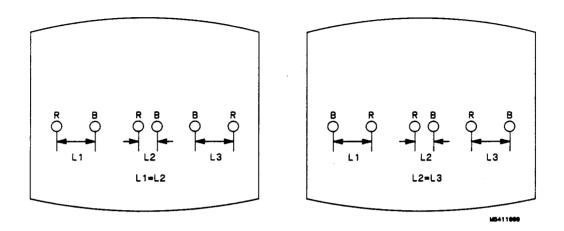

|    | 4-25.        | Color CRT Module Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-30 |

| 5. | REPLACEABLE  | E PARTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|    | <b>=</b> 4   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-1  |

|    | 5-1.         | Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-1  |

|    | 5-2.         | Parts List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-1  |

|    | 5-3.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-1  |

|    | 5-4.<br>5-5. | Exchange Assemblies Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-2  |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

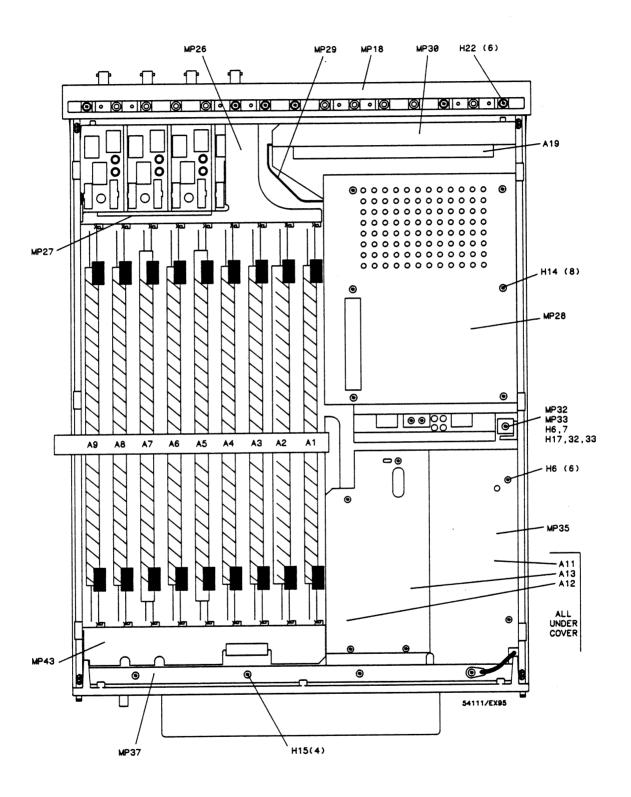

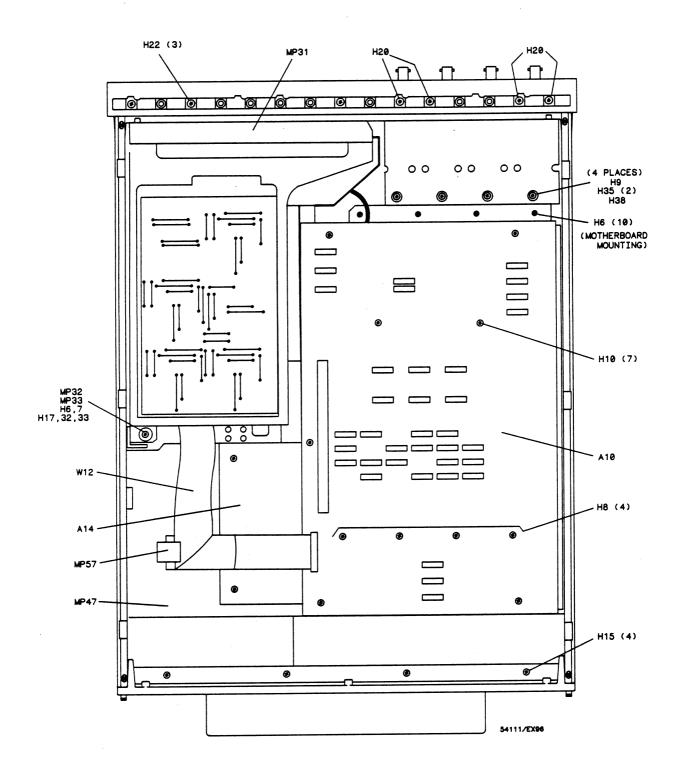

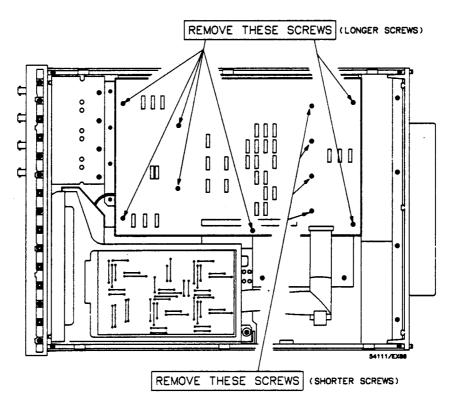

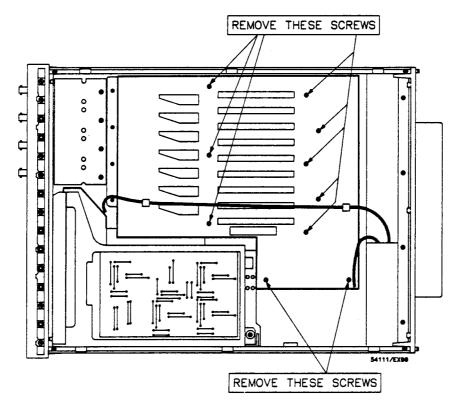

| 6A. | INSTRUMENT  | DISASSEMBLY                                        |        |

|-----|-------------|----------------------------------------------------|--------|

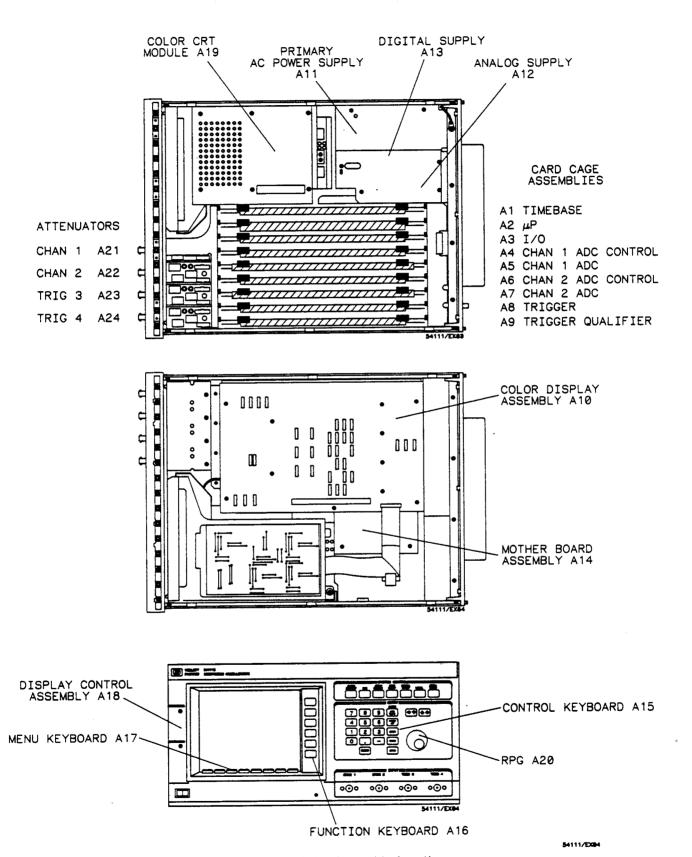

|     | 6A-1.       | Introduction                                       | 6A-1   |

|     | 6A-2.       | Safety Considerations                              | . 6A-1 |

|     | 6A-3.       | Tools Required                                     | . 6A-1 |

|     | 6A-4.       | Major Assembly Removal Procedures                  |        |

|     | 6A-5.       | Card Cage PC Assemblies                            |        |

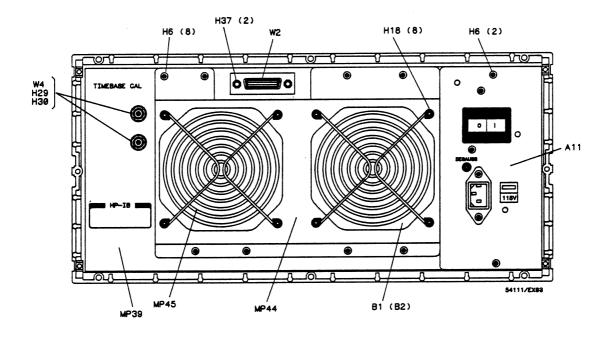

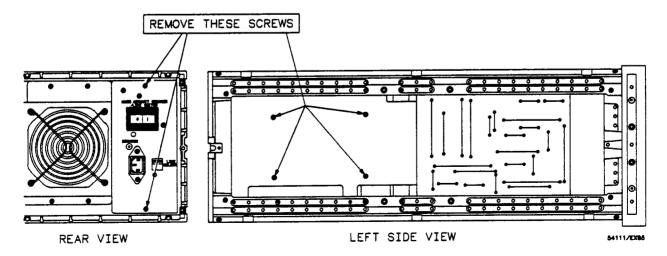

|     | 6A-6.       | Primary Power Supply                               | 6A-4   |

|     | 6A-7.       | Analog Power Supply                                |        |

|     | 6A-8.       | Digital Power Supply                               |        |

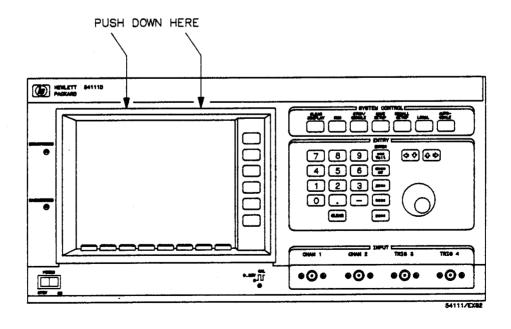

|     | 6A-9.       | CRT Bezel, Function and Menu Keyboards             |        |

|     | 6A-10.      | Front Panel, Control Keyboard, and Display Control |        |

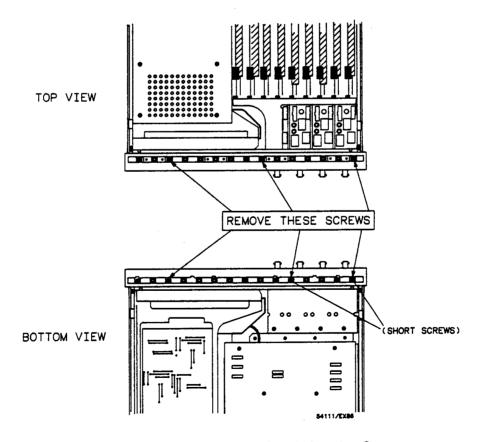

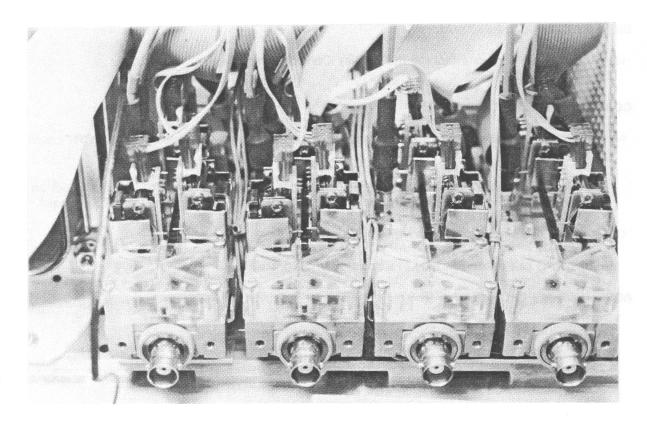

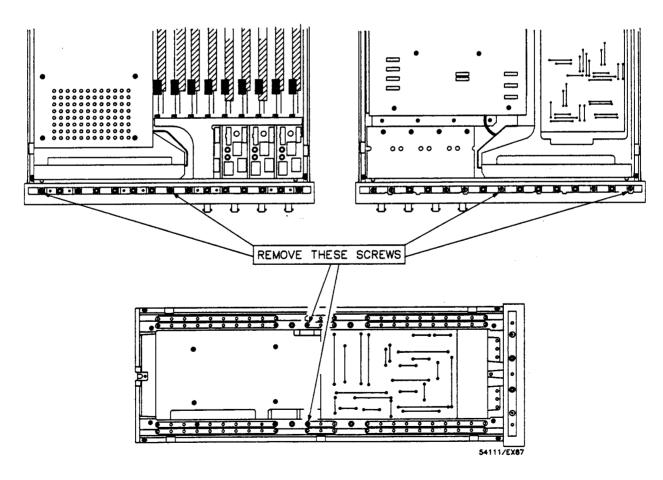

|     | 6A-11.      | Attenuators                                        | 6A-10  |

|     | 6A-12.      | Color CRT Module                                   | 6A-12  |

|     | 6A-13.      | Fans                                               | 6A-14  |

|     | 6A-14.      | Color Display Assembly                             | 6A-15  |

|     | 6A-15.      | Mother Board                                       | 6A-16  |

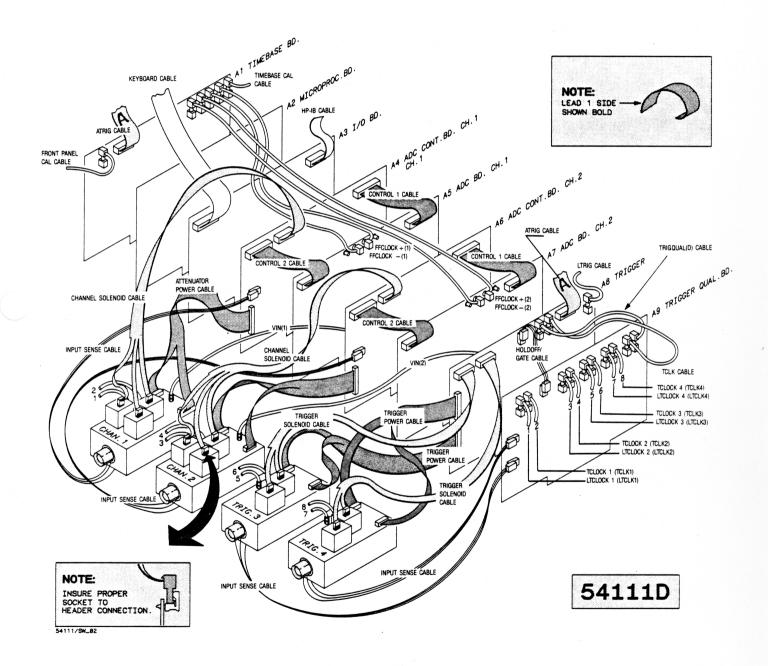

|     | 6A-16.      | Cabling Diagram                                    | 6A-17  |

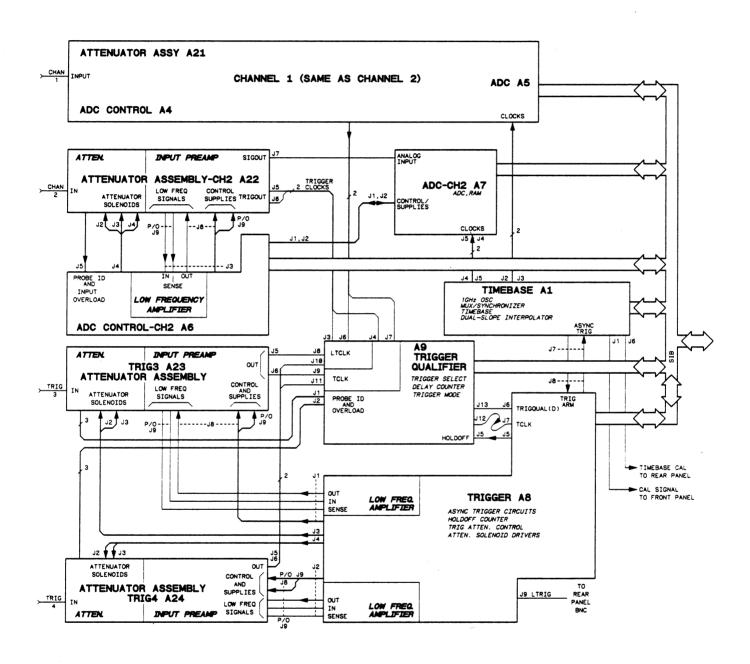

| 6B. | THEORY OF O | PERATION                                           |        |

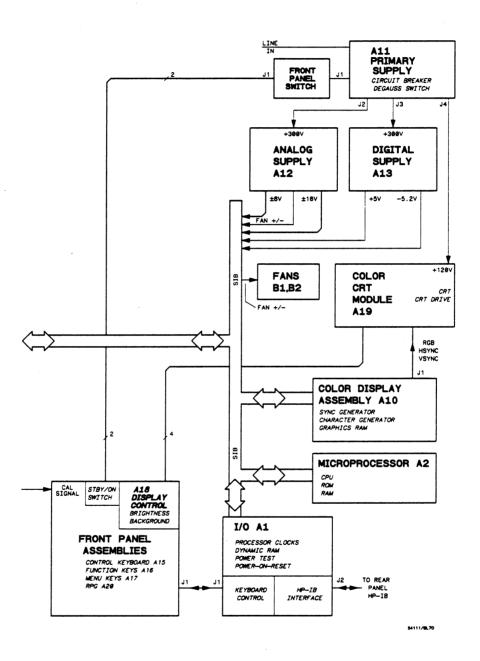

|     | 6B-1.       | Instrument Level Theory                            | 6B-    |

|     | 6B-2.       | Typical Data Acquisition Cycle                     |        |

|     | 6B-3.       | Acquisition                                        |        |

|     | 6B-4.       | Triggering and Sample Clocking                     |        |

|     | 6B-5.       | Instrument Control                                 |        |

|     | 6B-6.       | Power Supplies                                     | 6B-4   |

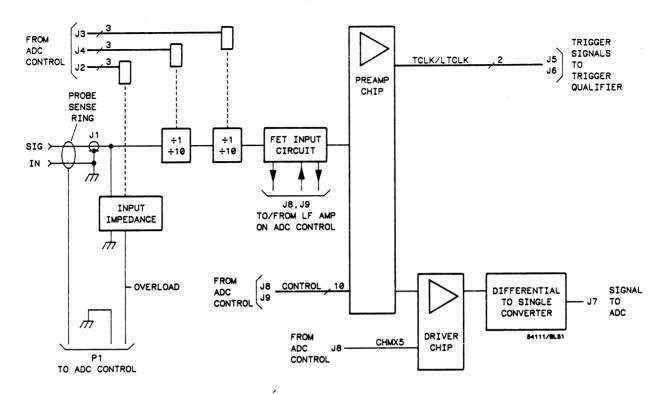

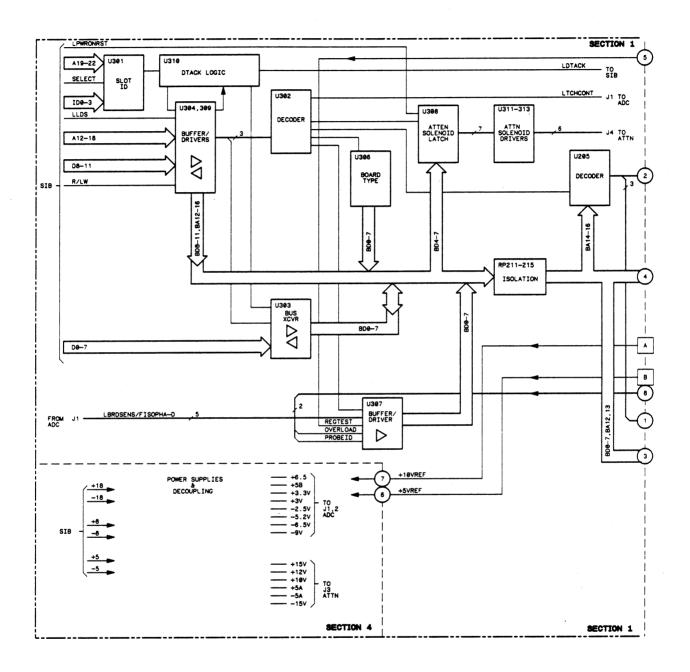

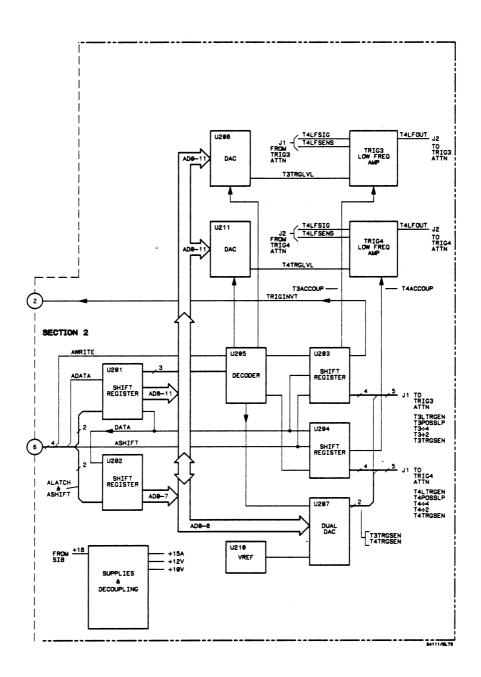

|     | 6B-7.       | Attenuator Assembly Theory                         |        |

|     | 6B-8.       | Channel Attenuators                                |        |

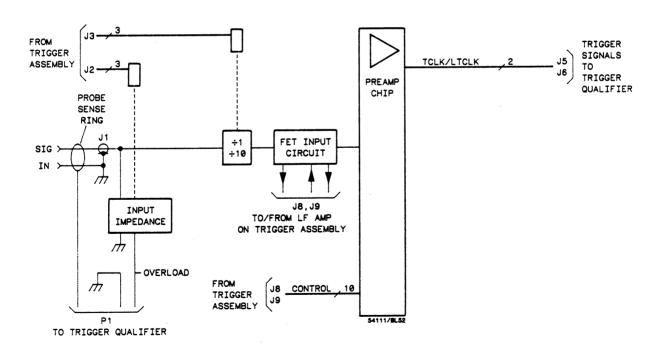

|     | 6B-9.       | Trigger Attenuators                                |        |

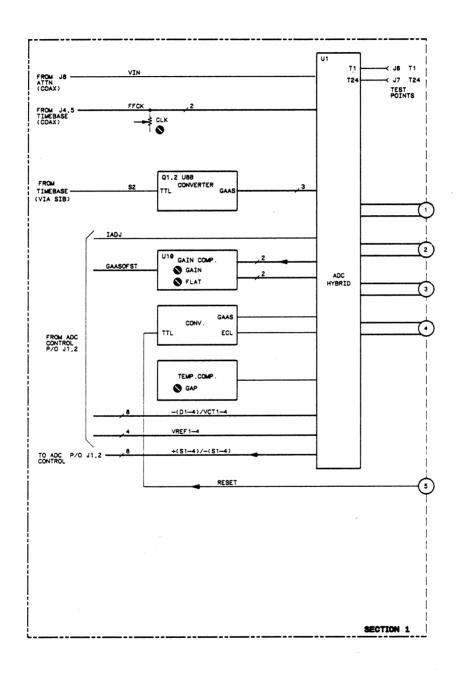

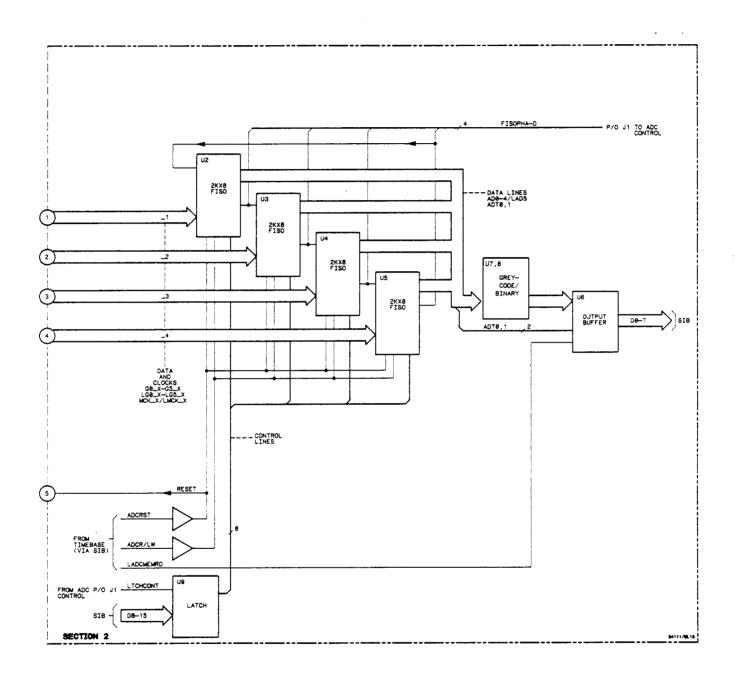

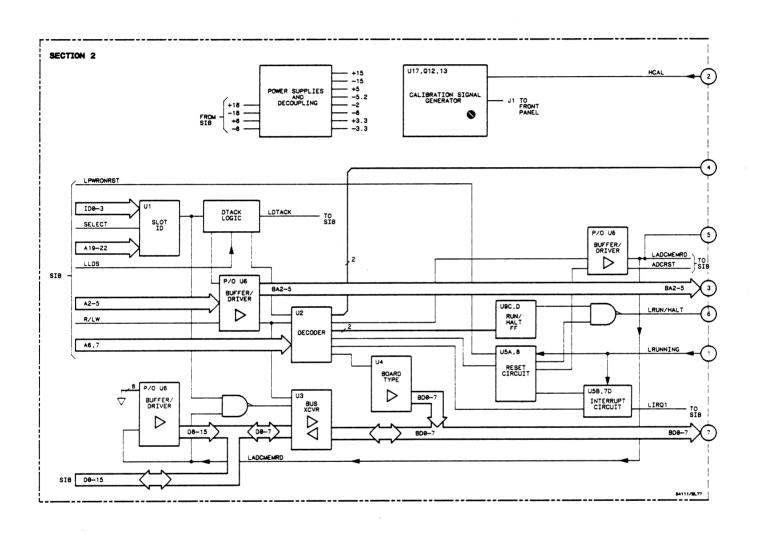

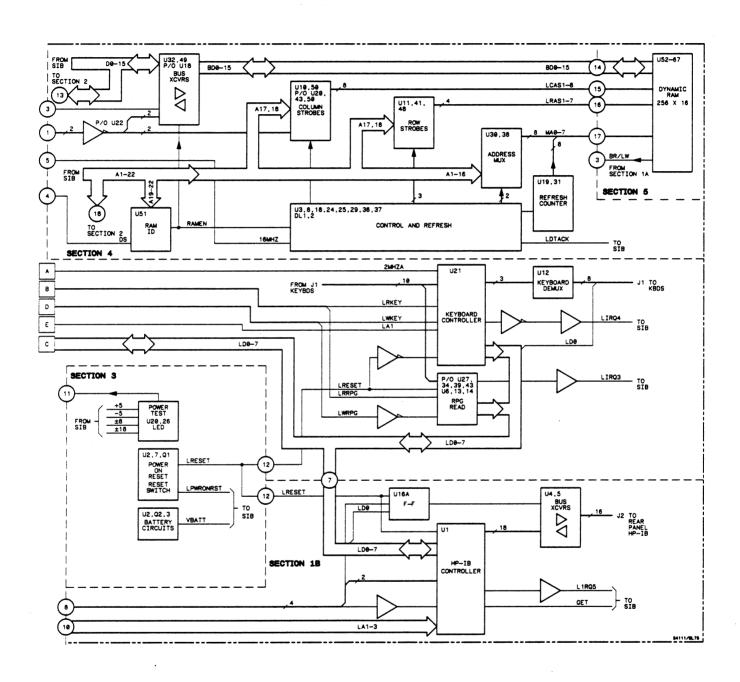

|     |             | ADC Assembly Theory                                |        |

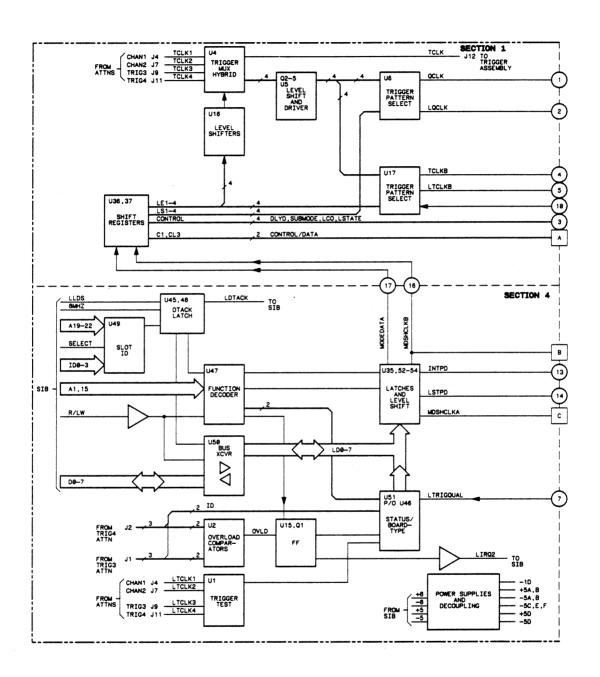

|     | 6B-11.      | ADC Control Assembly Theory                        | 6B-13  |

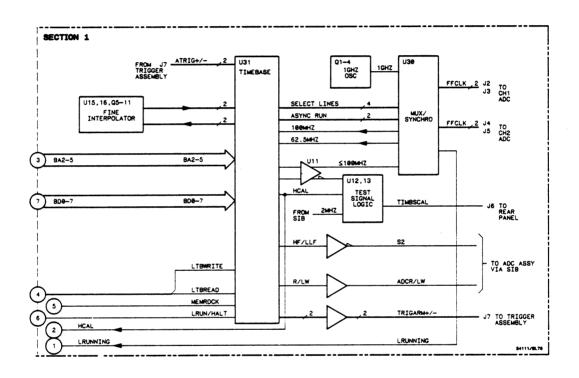

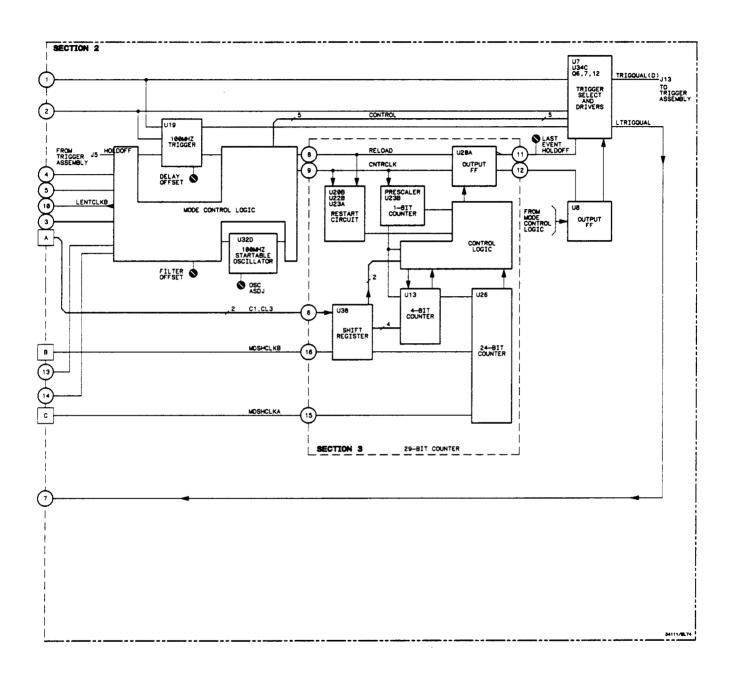

|     |             | Timebase Assembly Theory                           | 6B-17  |

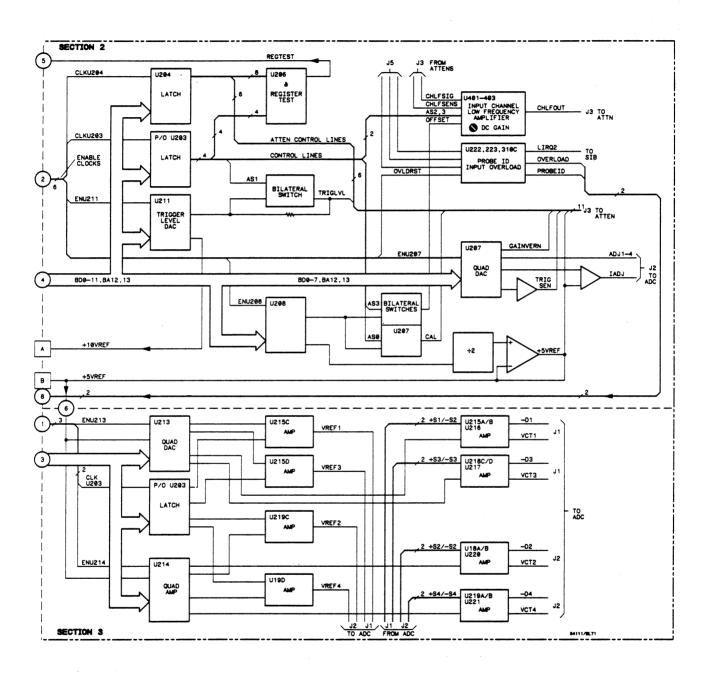

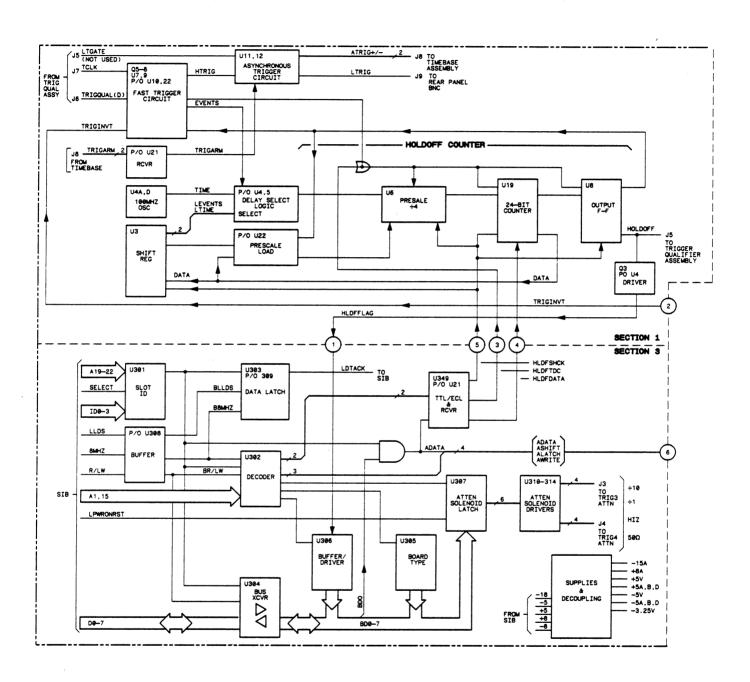

|     |             | Trigger Assembly Theory                            | 6B-2   |

|     |             |                                                    | 6B-25  |

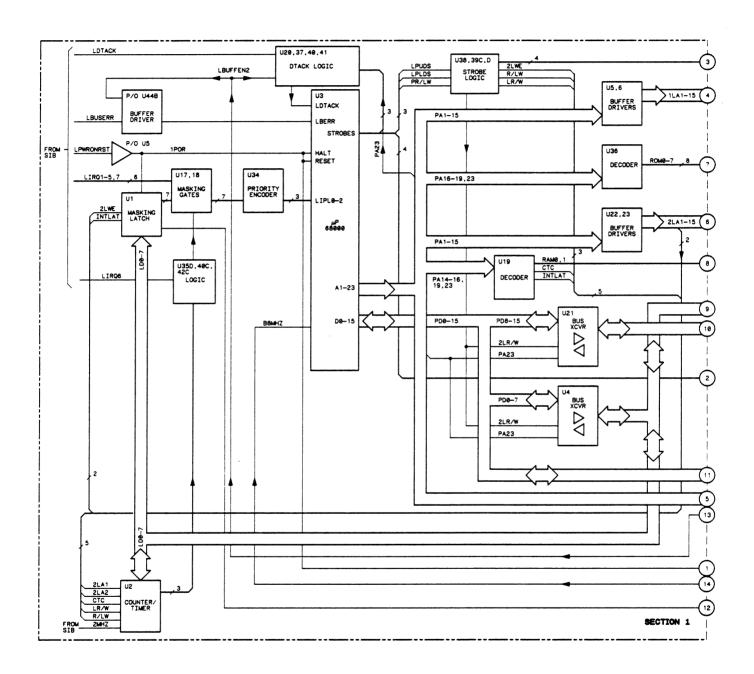

|     |             | Input/Output Assembly Theory                       | 6B-29  |

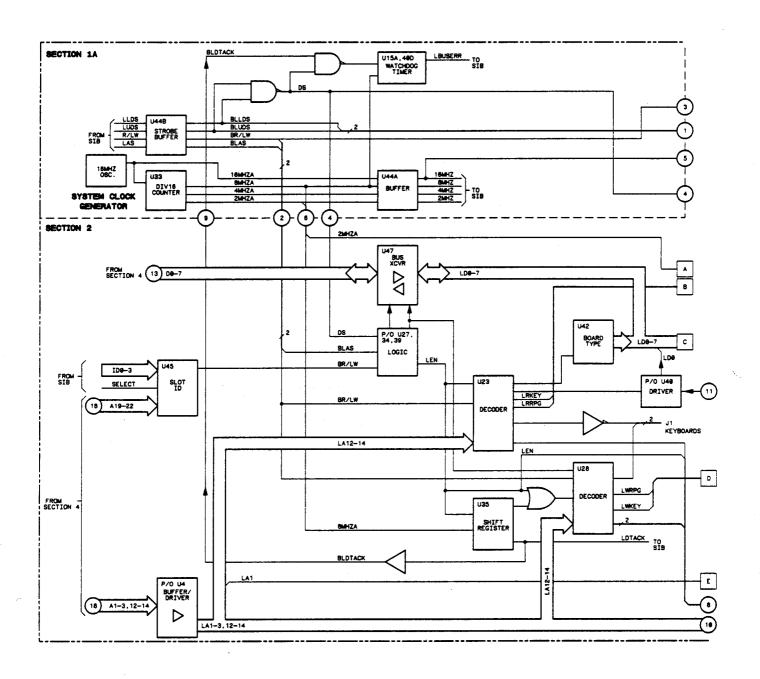

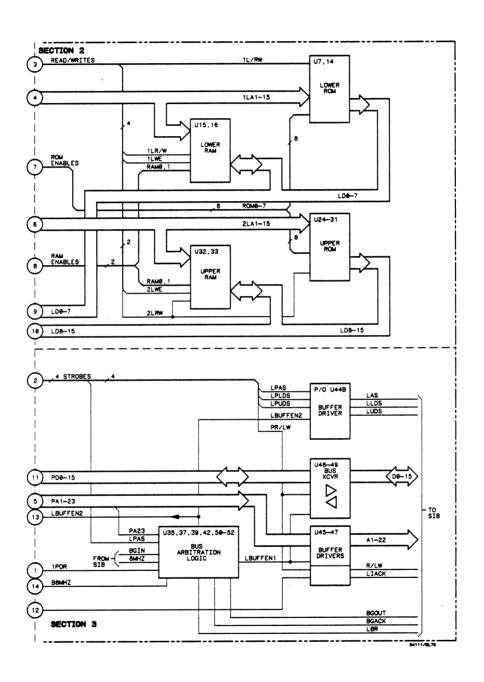

|     | 6B-16.      | Microprocessor Assembly Theory                     | 6B-33  |

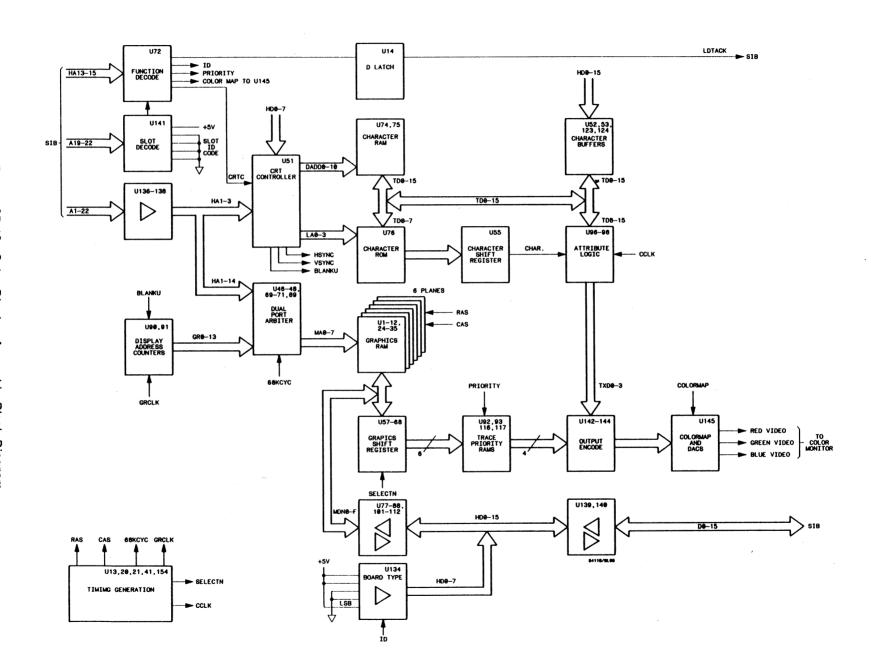

|     |             | Color Display Assembly Theory                      | 6B-37  |

|     |             | Power Supply Theory                                | 6B-39  |

|     | 6B-19.      | Primary Power Supply                               | 6B-39  |

| •   | 6B-20.      | Digital Power Supply                               | 6B-39  |

|     | 6B-21.      | Analog Power Supply                                | 6B-39  |

| 6C. | SERVICE MEN    | US/KEYS                            |       |

|-----|----------------|------------------------------------|-------|

|     | 6C-1.          | Introduction                       |       |

|     | 6C-2.          | Service Menus                      |       |

|     | 6C <b>-</b> 3. | One-Key Power Up                   |       |

|     | 6C-4.          | Two-Key Power Up                   |       |

|     | 6C-5.          | Cal Menus                          | 6C-2  |

|     | 6C-6.          | ADC Reference Cal                  |       |

|     | 6C-7.          | Probe Tip Cal                      | 6C-2  |

|     | 6C-8.          | Vertical Cal                       |       |

|     | 6C-9.          | Trigger Cal                        | 6C-2  |

|     | 6C-10.         | Timebase Cal                       | 6C-2  |

|     | 6C-11.         | Channel Skew                       | 6C-2  |

|     | 6C-12.         | Timebase Freq Cal                  | 6C-3  |

|     | 6C-13.         | Test Menu                          | 6C-3  |

|     | 6C-14.         | Repeat Loop/Run From Loop          | 6C-3  |

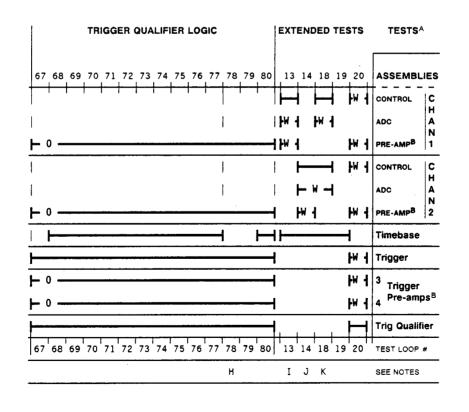

|     | 6C-15.         | Extended Tests                     | 6C-4  |

|     | 6C-16.         | Start/Stop Test                    | 6C-4  |

|     | 6C-17.         | Display Errors                     | 6C-4  |

|     | 6C-18.         | Display Configuration              |       |

|     | 6C-19.         | CRT Setup Menu                     | 6C-4  |

|     | 6C-20.         | Confidence Test                    | 6C-4  |

|     | 6C-21.         | Pattern                            | 6C-5  |

|     | 6C-22.         | Light Output                       |       |

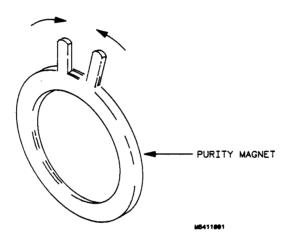

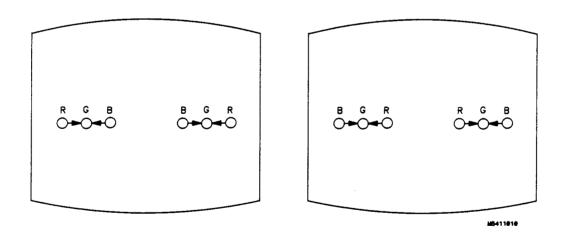

|     | 6C-23.         | Color Purity                       | 6C-5  |

| 6D. | SELF-TESTS/T   | ROUBLESHOOTING                     |       |

|     | •              |                                    |       |

|     | 6D-1.          | Introduction                       |       |

|     | 6D-2.          | Failure Indications                |       |

|     | 6D-3.          | Test Equipment Required            |       |

|     | 6D-4.          | One-Key Power Up                   |       |

|     | 6D-5.          | Two-Key Power Up                   | 6D-2  |

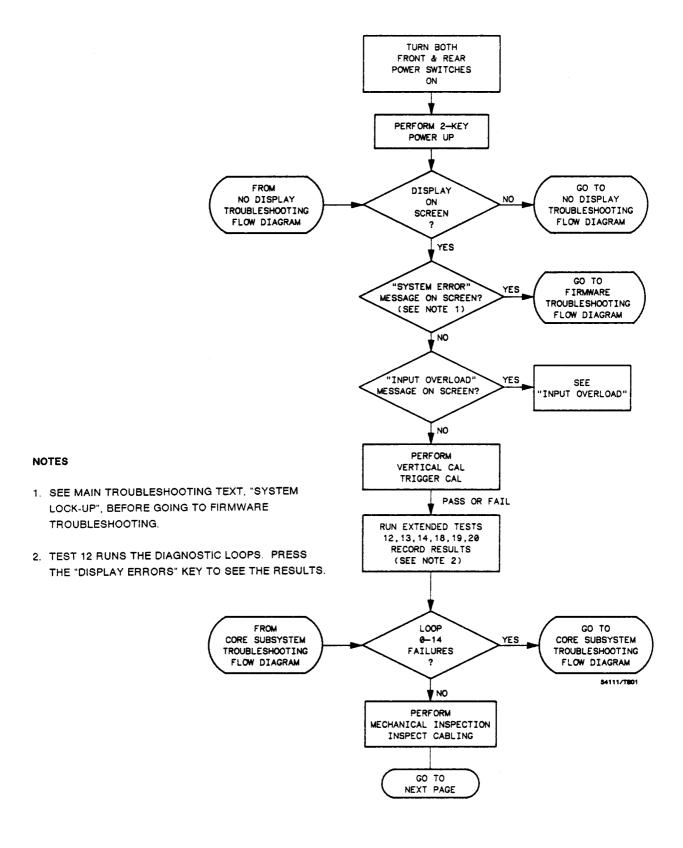

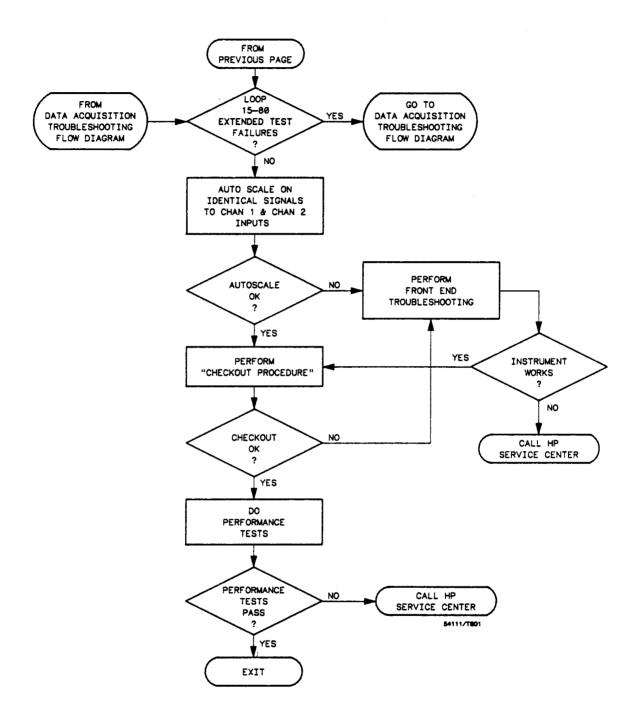

|     | 6D-6.          | Main Troubleshooting               |       |

|     | 6D-7.          | Power-up Self-Tests                |       |

|     | 6D-8.          | Instrument Warm-up                 |       |

|     | 6D-9.          | Connectors                         | 6D-3  |

|     | 6D-10.         | System Lock-up                     | 6D-3  |

|     | 6D-11.         | Input Overload                     |       |

|     | 6D-12.         | Intermittent Failures              |       |

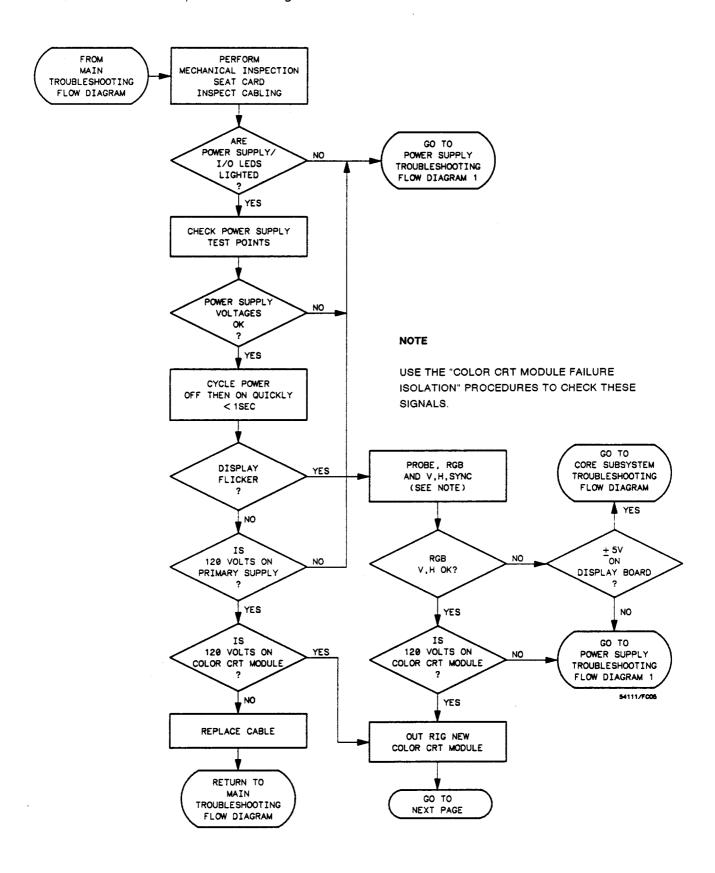

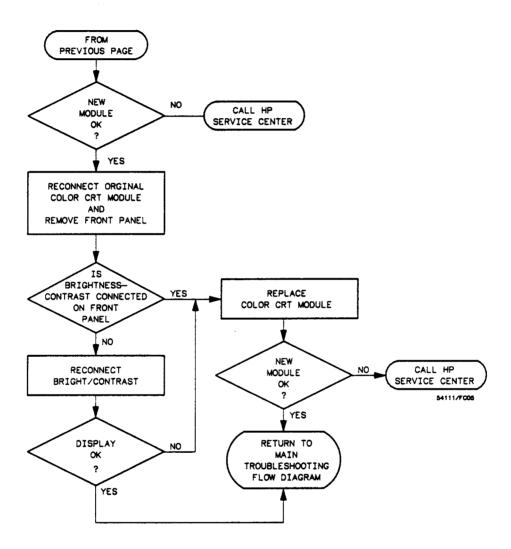

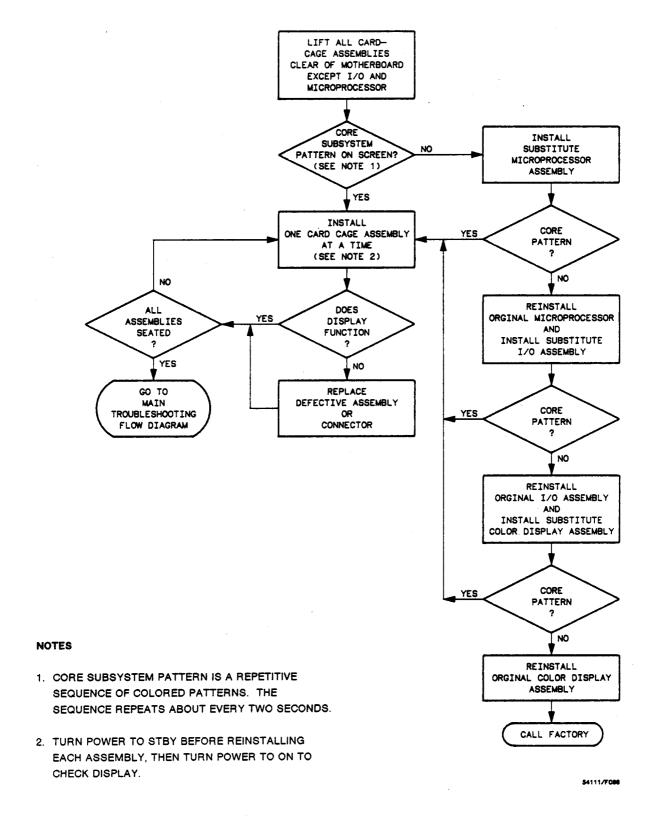

|     | 6D-13.         | No-Display Troubleshooting         | 6D-7  |

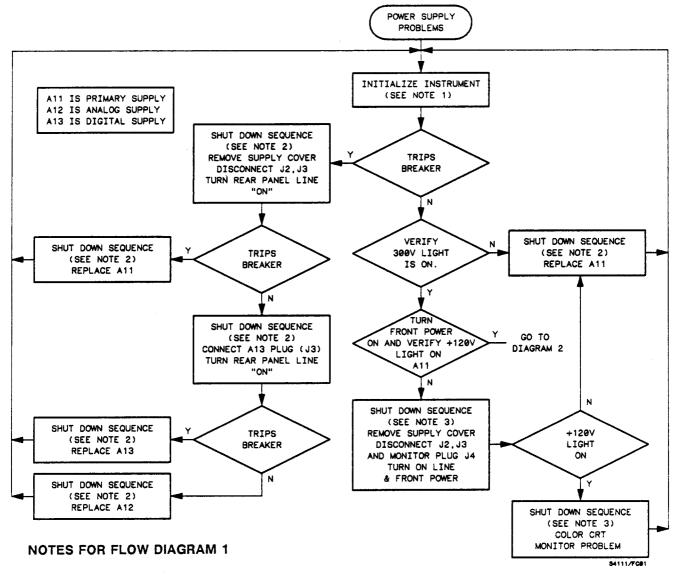

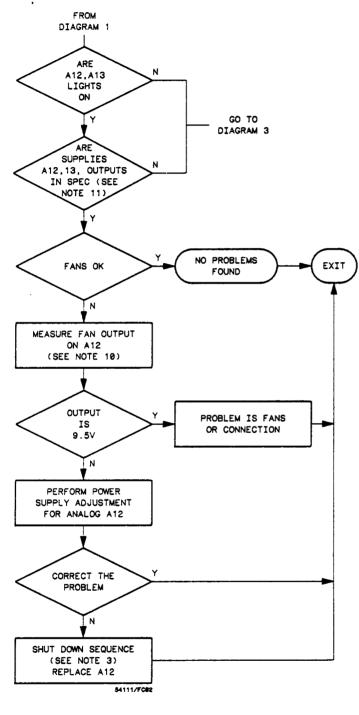

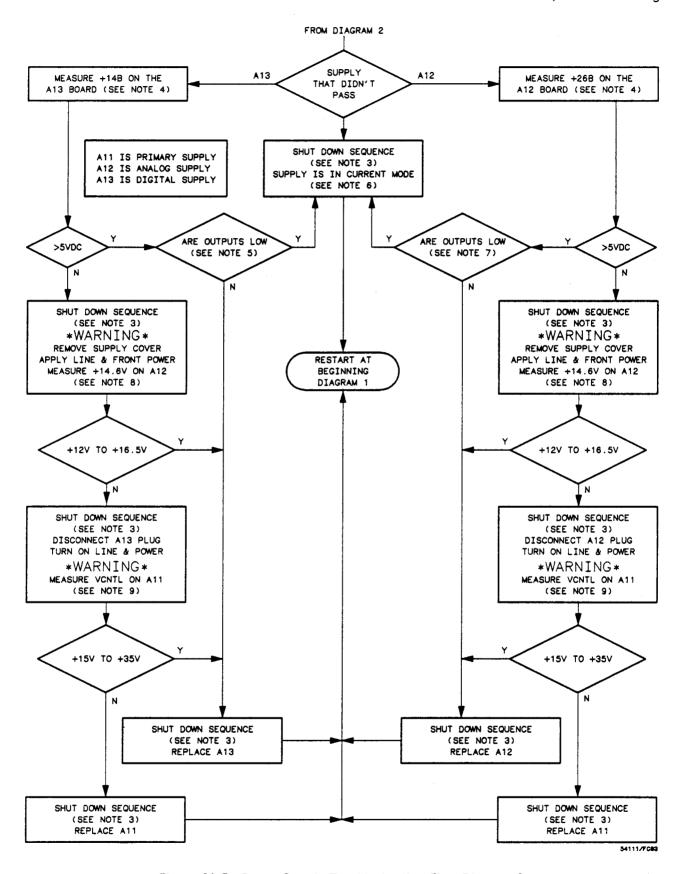

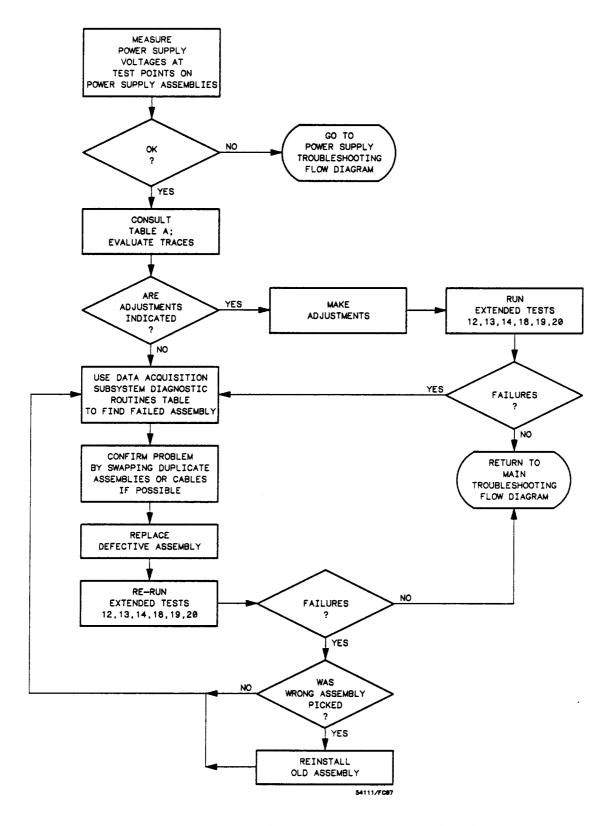

|     |                | Power Supply Troubleshooting       | 6D-11 |

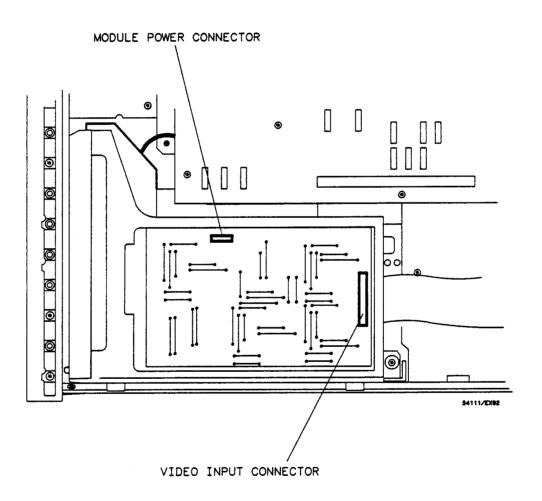

|     | 6D-15.         | Color CRT Module Failure Isolation | 6D-16 |

#### 6D. SELF-TESTS/TROUBLESHOOTING (CON'T.)

| 6D-16. | Troubleshooting Procedure                              | 6D-16 |

|--------|--------------------------------------------------------|-------|

| 6D-17. | Incorrect Display Color                                | 6D-18 |

| 6D-18. | Module Outrigging Procedure                            | 6D-18 |

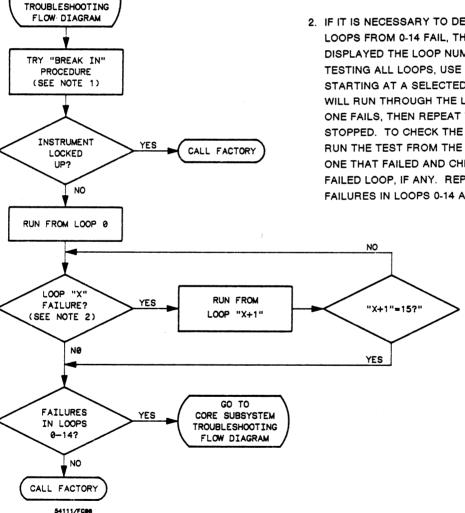

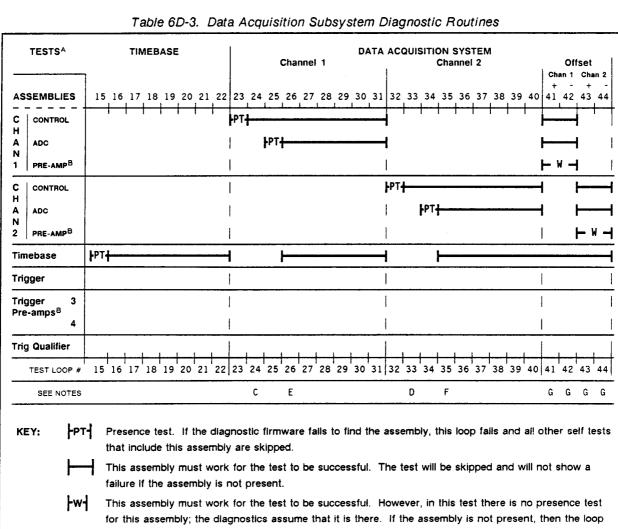

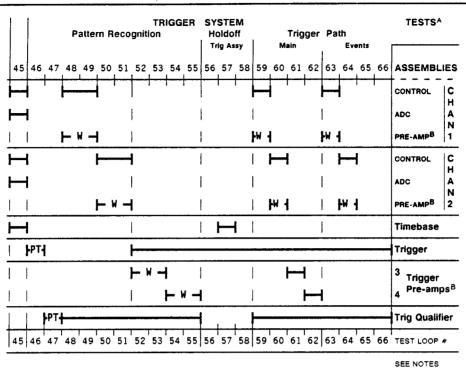

| 6D-19. | Firmware Troubleshooting                               | 6D-19 |